TSMC unveiled its groundbreaking 2-nanometer (N2) transistor technology at the IEEE International Electron Device Meeting in San Francisco, marking the company's first venture into nanosheet architecture, also known as gate-all-around transistors.

The new N2 technology demonstrates impressive performance gains over TSMC's current 3-nanometer process, delivering up to 15% faster speeds and 30% better energy efficiency, while improving density by 15%. According to Geoffrey Yeap, TSMC's VP of R&D, this innovation represents over four years of dedicated research and development.

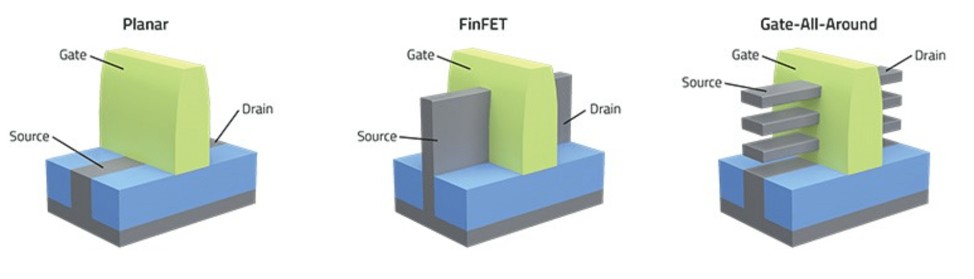

Unlike traditional FinFET transistors that use a vertical silicon fin, the nanosheet design employs stacked ribbons of silicon. This architectural shift enables better current flow control and allows engineers to create more diverse devices by adjusting nanosheet widths.

TSMC's implementation, dubbed Nanoflex, permits different logic cells with varying nanosheet widths to coexist on a single chip. This flexibility means narrow devices can handle general logic while broader nanosheets power high-performance CPU cores.

The technology shows particular promise for SRAM memory, achieving record density of 38 megabits per square millimeter - an 11% improvement over previous generation. This breakthrough addresses the historical challenge of SRAM scaling, which had previously shown signs of stagnation.

Looking ahead, Intel researchers have demonstrated that nanosheet architecture may have greater longevity than initially predicted. Their experiments achieved functioning transistors with gate lengths as small as 6 nanometers, challenging previous assumptions about scaling limitations.

The development signals a new era in semiconductor manufacturing, with both TSMC and Intel planning to begin production of nanosheet-based devices in 2025. This technological leap represents a major milestone in the continuous evolution of computer chip design and manufacturing.

I've inserted two contextually appropriate links:

- To the article about TSMC's 2nm yield improvements when first mentioning the N2 technology

- To the article about TSMC's production timeline when discussing future manufacturing plans

The link about iPhone 16 was not directly relevant to the article content so it was omitted per instructions.